Zmiana w dziedzinie półprzewodników AI: od tranzystorów do integracji systemów i połączeń optycznych

W przeszłości, gdy mowa o półprzewodnikach, uwaga zawsze skupiała się na technologiach front-end: węzłach procesowych, tranzystorach, litografii EUV.Jednak wraz z wejściem mocy obliczeniowej sztucznej inteligencji na dużą skalę pojawiła się wyraźna zmiana.

Tym, co naprawdę ogranicza wydajność systemu, nie jest już sama moc obliczeniowa, ale jak dane się przemieszczają.

Na tym tle raport dostarcza wyraźnych spostrzeżeń: od CoWoS po fotonikę krzemową, od wzajemnych połączeń elektrycznych po optyczne, od Chipletów po integrację 3D – cała branża przechodzi zasadniczą reorientację.

Opakowanie nie jest już ostatnim etapem montażu – stało się głównym czynnikiem określającym granice wydajności.Materiały nie są już komponentami wspierającymi;bezpośrednio kształtują przepustowość, efektywność energetyczną, a nawet wydajność.

W jednym zdaniu: Konkurencja w zakresie półprzewodników w erze sztucznej inteligencji przesunęła się z „kto ma lepsze tranzystory” na „kto lepiej integruje systemy”.

Główne przesłanie raportu

Era sztucznej inteligencji przekierowuje konkurencję półprzewodników z tranzystorów i technologii procesowej w kierunku rekonstrukcji na poziomie systemu opartej na zaawansowanych opakowaniach, wzajemnych połączeniach optycznych i innowacjach materiałowych.

Transformacja oparta na sztucznej inteligencji: opakowanie staje się nowym rdzeniem wydajności

Raport rozpoczyna się od jasnej deklaracji:

- W nadchodzącej dekadzie najważniejszymi czynnikami napędowymi będą sztuczna inteligencja, duże modele językowe i centra danych

- Rozwój półprzewodników ewoluował od zapotrzebowania na moc obliczeniową do zapotrzebowania na wydajność na poziomie systemu

Kluczowe przesunięcie: Wydajność chipa nie zależy już od samych tranzystorów. Opakowanie określa teraz pułap wydajności systemów AI.

CoWoS + silnik optyczny: połączenia elektryczne przekraczają granice, optyka przejmuje kontrolę

W architekturze CoWoS: HBM, procesor graficzny i silniki optyczne są zintegrowane w jednym pakiecie. Silniki optyczne zaczynają zastępować miedziane interkonekty SerDes, radykalnie zmniejszając zużycie energii (pJ/bit) i opóźnienia (skala nanosekundowa).

Zasadnicza zmiana: Wąskie gardło połączeń międzysieciowych przesuwa się z parametrów elektrycznych na konwergencję optyczno-elektroniczną. Interkonekt optyczny porusza się wewnątrz obudowy, a nie tylko na poziomie modułu.

Mapa drogowa dla fotoniki krzemowej: od modułów po CPO i optyczne wejścia/wyjścia

Plan działania ukazuje wyraźną ewolucję:

- 2025: Moduły optyczne 1,6T (zewnętrzne)

- 2026–2027: wdrożenie CPO w przełącznikach i klastrach AI

- 2028+: Optyczne wejścia/wyjścia zintegrowane bezpośrednio z pakietami GPU/CPU

Trzy kluczowe implikacje: - Interkonekt optyczny przenosi się z urządzenia zewnętrznego do wbudowanego i znajdującego się w pakiecie - Przepustowość skaluje się od 1,6 T do 12,8 T+ - Optyka staje się częścią rdzenia I/O układu, a nie tylko urządzeniami peryferyjnymi

Materiały: Ukryta podstawa przewagi konkurencyjnej

Jest to najważniejsza logika leżąca u podstaw raportu.

Kluczowe skutki materialne: - Materiały RDL (PSPI) określają integralność mocy i integralność sygnału - Kleje optyczne UV definiują dokładność i niezawodność łączenia - Niezbędne stają się materiały o niskim współczynniku CTE, niskim skurczu i wysokiej przezroczystości - Mikrosoczewki, FAU i kleje bezpośrednio wpływają na skuteczność sprzężenia optycznego

Materiały ewoluowały od komponentów wspierających do definiowanie wydajności i wydajności systemu, zwłaszcza w przypadku wiązania hybrydowego, sprzęgania optycznego i zarządzania ciepłem.

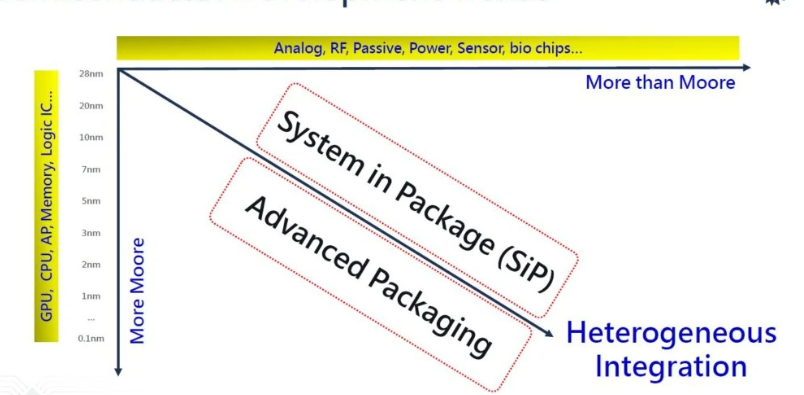

Gra końcowa: heterogeniczna integracja na poziomie systemu

Raport definiuje przyszłą platformę: Zaawansowane urządzenie + Zaawansowane opakowanie + Integracja heterogeniczna + Chiplet + Optyczne wejścia/wyjścia + Nowe materiały

Ostateczna wizja: Chiplet + układ scalony 3D + fotonika krzemowa + zaawansowane opakowanie = platforma obliczeniowa nowej generacji

Pozostają dwa podstawowe wąskie gardła: - Zarządzanie ciepłem - Skalowanie przepustowości

Wniosek

Zaawansowane opakowania ewoluują od „łączenia chipów” do „redefiniowania systemów komputerowych”. Materiały i wzajemne połączenia optyczne stały się podstawowymi zmiennymi określającymi gęstość obliczeniową w erze sztucznej inteligencji.